微机原理期末复习

补码:取反加一。

可编程芯片,它们是

- 8259A:中断控制器

- 8255A:并行通信

- 8253:定时器

- 8251:串行通信

- 8237:DMA控制器

8086处理器

FLAGS

- 单步中断允许TF=1;可屏蔽中断允许IF=1;串操作从低地址到高地址DF=0.

- 加减法最高位进位借位CF=1;最高位与次高位进位不同时OF=1;不论是字节运算还是字运算,当低8位1的个数为偶数时PF=1;不论是字运算还是字节运算,当低4位向高位进位或借位时AF=1(用于BCD码调整);SF与运算的最高位相同;结果为0时ZF=1.

地址锁存器 8282 / 74LS373. 对于8282,8位,锁存使能,锁存触发下降沿(来自ALE的下降沿)。

总线驱动器 8286 / 74LS245. 对于8286,8位,芯片使能,输入输出方向控制.

HOLD外设总线请求;HLDA总线请求应答;DT/ 接8286的T控制数据总线方向;接8286使能,控制数据使能;NMI上升沿响应;INTR高电平响应(IF=1时);RESET清零FLAGS IP DS SS ES和指令队列,CS置FFFF;READY表示储存器或IO准备好;CLK占空比1:3,时钟信号可以来自8284A.

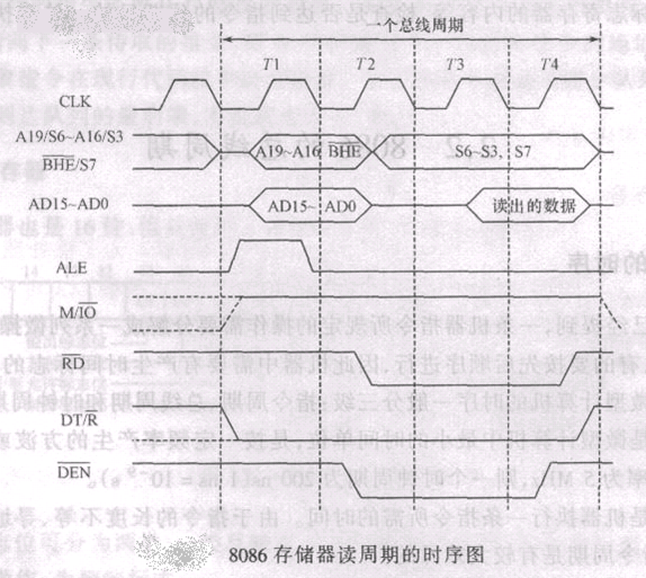

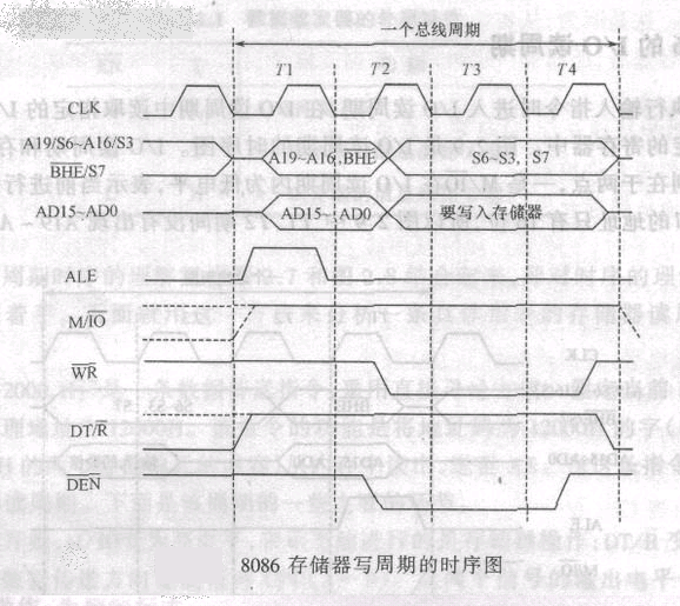

8086的基本总线周期

- T1地址周期,T2缓冲周期,T3数据周期,T4结束周期。

- 8086在T3前沿检测READY,如果是低电平则插入Tw,Tw内各输出引脚保持T3状态;此后每个Tw前沿检测READY.

- 读出数据时间为N个时钟周期,则在T3和T4之间插入N-1个Tw.

最小模式读内存时序

最小模式写内存时序

8086内存的FFFF0~FFFFF放了系统复位代码,00000~003FF共Bytes的空间存放了256个中断向量,低字放IP,高字放CS.

8086的IO空间是0000~FFFF共64K个端口。

指令系统与汇编语言

偏移地址又称有效地址EA,段基址和偏移地址统称逻辑地址。

储存器寻址

- 直接寻址默认在数据段

[20E9H];段超越前缀ES:[20E9H]。 - 寄存器间接寻址

BX、SI、DI默认在数据段;BP默认在堆栈段。 - 寄存器相对寻址

20E9H[SI]或[SI+20E9H],默认段寄存器与上面一样。 - 基址变址寻址

[BX][SI]或[BX+SI],必须一个基址寄存器+一个变址寄存器,BP默认堆栈段,BX默认数据段。 - 相对基址变址类似。

- 直接寻址默认在数据段

IO寻址

- 00~FF的地址可以由立即数给出;0000~FFFF的地址只能由

DX给出。

- 00~FF的地址可以由立即数给出;0000~FFFF的地址只能由

转移寻址

JMP 20E9:2018(CS)=20E9H(IP)=2018H.JMP F(IP)=000FH.JMP SHORT label8bits disp.JMP NEAR PTR label16bits disp.JMP FAR PTR label段间转移。JMP AX(IP)=(AX).JMP WORD PTR [BX](IP)=[BX].JMP DWORD PTR [BX](CS)=[BX+2](IP)=[BX].- 对于无符号数用

JBJNBJNAJA系列(above、below);对于有符号数用JLJNLJNGJG系列(less、greater)。 - 所有的条件转移指令都是段内直接短转移(8bits disp)。

LOOPLOOPZLOOPNZ所有的循环控制转移都是短转移(8bits disp)。CALL labelCALL [BX]段内直接调用和间接调用都是近调用(16bits disp)。CALL FAR PTR labelCALL DWORD PTR [BX]段间直接调用和间接调用都是远调用。- 中断调用是远调用。

RETIRETRET不恢复标志位(CALL不压FLAGS);IRET都是远转移,且恢复标志位(INT将FLAGS压栈)。

MOVDST不能是CS;DST和SRC不能同时为段寄存器;立即数不能直接传入段寄存器。XCHG不可以用段寄存器。XLAT隐式用AL和BX:(AL)=DS:[BX+AL].PUSH和POP都是字操作,不可以用字节;POP不可以到CS。INC和DEC影响除了CF外的标志位。CMP OP1, OP2按照OP1-OP2的结果设置标志位。MUL OPIMUL OP将OP乘到AX或AL上,结果放在(DX,AX)或AX中;若乘积的高半部分存了有意义的数字,则OF=CF=1.DIV OPIDIV OP对于字节除法AX/OP,AL存商,AH存余数;对于字除法(DX,AX)/OP,AX存商,DX存余数;余数的符号与被除数的符号相同;标志位无定义。CBWCWD根据AL或AX的最高位扩展到AH和DX,使作为被除数。TEST OP1, OP2按照AND OP1, OP2的结果设置标志位,影响SF、ZF、PF.SHLSHRSALSARSHL和SAL是一样的,低位补零,高位进CF;SHR高位补零,低位进CF;SAR高位不变,低位进CF. 如果移位大于1位,需要用CL存位数。ROLRORRCLRCRROL和ROR循环的位同时被复制到CF;RCL和RCR高位或低位进CF,原CF进入循环。MOVSBMOVSWSTOSBSTOSWLODSBLODSW源串在数据段,目的串在附加段;STOS和LODS都隐含使用AL或AX寄存器。CMPSBCMPSWSCASBSCASWSMPS比较源串和目的串当前字或字节;SCAS比较AL或AX与目的串当前字或字节。REPREPZREPNZ加在串指令前的循环操作前缀,计数器CX.LOCK总线封锁前缀,使这条指令执行完之前引脚为低电平。INT- 功能号放在AH里面。

- 05~1F是BIOS中断调用;20~3F是DOS中断调用。

- AH=02H,INT 21H:将DL中的字符送标准输出流。

- AH=01H,INT 21H:键盘输入字符存入AL中。

- DL=0FFH,AH=06H,INT 21H:不等待键盘输入,如果无输入,ZF=1;如果有输入,ZF=0,字符存AL.

- AH=09H,INT 21H:将DX(偏移地址)指向的字符串输出到console,以'$'结束。

- AH=0AH,INT 21H:读入字符串,以回车结束,存入DX指向的buffer,[DX]预存了最大串长,[DX+1]将存入实际串长,字符串从DX+2开始存。

- AH=4CH,INT 21H:返回DOS系统。

储存器编制

存储容量:基本单元数(芯片字数) (位数/芯片字)

存取速度

- 存取时间:从CPU给出有效的地址到存储区读写操作完成需要的时间。

- 存取周期:两次访问的最小时间间隔,略大于存取时间。

两个储存器层次

- Cache-主存:为提高CPU访问主存的速度,由专门硬件(Cache控制器)实现,对程序完全透明。

- 主存-辅存:为弥补主存容量不足,还可以构成“虚拟存储去”,需要操作系统和MMU的支持。

半导体存储器分类

- TTL双极性,MOS单极型。

- RAM,ROM.

- 易失性与非易失性。

单地址译码——线性储存块;双地址译码——储存矩阵。

2114是bits的SRAM,6264是bits的SRAM. 每个SRAM单元由6个MOS管储存1bit信息。速度快,功耗大,成本高。

2164A是bits的DRAM. 每个DRAM单元由一个MOS管和电容储存1bit信息,由于电荷泄露,需要定期刷新。有8个地址引脚,需要先给行地址,再给列地址。

DRAM刷新按行进行。

DRAM集成度高,功耗低,需要DRAM控制电路。

74LS138是3-8译码器,74LS139是双2-4译码器。3-8译码器的ABC依次对于低位到高位。

片选方法

- 全译码:所有高位地址线都要参与译码,每个储存单元的地址是唯一的。

- 部分译码:有些高位地址不参与译码(悬空),存在地址重叠现象。

- 线选法:直接用地址线选通. 存在地址不连续的现象。

- 分奇体和偶体时,用A0(低有效)选择偶体,用选择奇体。

Cache的映像方式:直接映像、全相联映像、组相联映像。

IO与中断

IO接口电路必须”输入要三态、输出要锁存“。还要对信号的速度、电平、形式、格式进行匹配。还可以提供外设的状态信号和中断控制逻辑。需要进行地址译码。提供可编程功能。

IO接口交换三种信息:数据信息、状态信息、控制信息。

编址方式有独立编址和统一编址两种,各有优劣,8086采用内存IO独立编址。

PC机使用低10位地址寻址IO端口,地址范围0000~03FF. 高位地址产生片选信号,低位地址选择片内端口。

CPU与外设间数据传送方式

- 程序直接控制传送方式:无条件传送、程序查询传送。

- 中断控制传送方式。

- DMA控制传送方式,需要DMAC支持。

中断源:能发出中断申请的事件称为中断源,处理器内中断源引发的中断称为内中断,处理器外引发的中断称为外中断。

中断过程:中断请求、中断源识别、中断响应、断点保护、现场保护、中断服务、现场恢复、中断返回。

中断判优(仲裁):软件查询方式、简单硬件方式(菊花链)、专用控制芯片。

非屏蔽中断是外部中断,中断类型码是02H;可屏蔽中断类型码08H~0FH.

除了单步中断(01H)外,所有的内部中断都无法禁止,因此软中断不能通过清零IF标志位来禁止。

8086的中断响应优先级(从高到低)

内部中断

- 除法错(00H)

- INT n

- INTO 溢出中断(04H)

- 断点中断(03H)

NMI(02H)

INTR 可屏蔽请求

单步中断(01H)

实际上在响应内部中断并保护断点之后,还要检测是否是NMI、是否是单步中断,因此执行中断服务程序的优先级是NMI和单步中断更高。

内部硬中断和NMI由硬件电路产生中断类型码,软中断由指令机器码产生中断类型码,可屏蔽中断由8259在收到第二个有效后将中断类型码发送到数据总线上。

启动时,BIOS和操作系统将非用户中断服务程序的入口地址填入中断向量表。用户定制的中断服务随后装入。

保护断点:FLAGS入栈;TF进暂存器;清TF、IF;CS入栈,IP入栈;查表,更新CS、IP。判断是否由NMI,有的话重新执行保护断点(注意这时暂存器也被清零);判断是否暂存器为1,是的话重新执行保护断点。

用户中断服务程序的编制

保存当前中断类型码n的服务程序

1MOV AL, n2MOV AH, 35H3INT 21H于是n的初始服务程序段基址放在ES中,偏移地址放在BX中。可以将这两个地址保存到内存里,回头再调回来。

关中断

CLI.填入新的中断类型码n的服务程序,假设我们编写的服务程序标号为LABEL. 我们先将其段基址放进DS,偏移地址放进DX.

xxxxxxxxxx31MOV AL, n2MOV AH, 25H3INT 21H就把(DS,DX)填入了n对应的中断向量表单元。

开中断

STI.在我们编写的服务子程序中,注意保护完现场后要开中断,即允许中断嵌套。恢复现场前要关中断。然后执行

xxxxxxxxxx21MOV AL, 20H2OUT 20H, AL向8259的控制端口写EOI控制字。最后开中断,用IRET返回。

最后我们用之前保存在内存中的初始服务程序地址恢复中断向量表。

可编程IO接口芯片

8259A 中断控制器

8路IRQ,级联最多可到64路。8位数据总线。

A0用于选择寄存器。

IMR中断屏蔽寄存器,ISR当前服务寄存器,PR中断优先级裁决器,IRR中断请求寄存器。

工作方式

中断触发

- 边沿触发:IRQ的上升沿作为触发,高电平至少保持到第一个负脉冲之前。80x86采用这种方式。

- 电平触发:IRQ的高电平作为触发,应及时撤销高电平。

中断嵌套

- 一般全嵌套:只允许高优先级中断低优先级,禁止同级。

- 特殊全嵌套:还允许同级。

优先级

- 固定优先级:IRQ0最高,IRQ7最低,是默认的方式。

- 优先级自动循环:一个服务完了优先级自动将为最低,其它的服务优先级依次上升,相当于等优先级。

- 优先级特殊循环:规定一个初始IRQn优先队列,再循环。

中断屏蔽

- 普通屏蔽:将IMR中相应位置置1.

- 特殊屏蔽:中断服务程序中,该中断对应的ISR被清零,IMR置位,此时所有其它中断都可以被响应,不论优先级。

中断结束

- 普通中断结束:中断服务结束前,CPU向8259发送EOI命令字,清除ISR中优先级最高的置位。

- 自动中断结束:第二个后自动EOI.

- 特殊中断结束:特殊屏蔽方式中,CPU发特殊命令字,指明哪一位ISR被复位。

初始化按照ICW1到ICW4的顺序,其中ICW2指定8259A的中断类型码的高五位,一般是08H,低3位自动填入。

8255A 并行接口芯片

ABC3路,每路8位。分为A组和B组。A组包括PA7-PA0和PC7-PC4;B组包括PB7-PA0和PC3-PC0.

8位数据总线,A0和A1选择片内端口。

工作方式

方式0:ABC口都可以设置,基本输入输出,单向,输出锁存,输入三态缓冲无锁存。适用于无条件数据传输。

方式1:AB口都可以设置,利用C口的某些位(AB口各分3位)作为应答联络线,单向,输入输出都有锁存,C口剩余位还可以作为方式0使用。适用于中断、查询方式传输。

- 方式1输入:应答联络线包括外设准备好、输入锁存器满、中断请求和是否允许发出中断请求。

- 方式1输出:应答联络线包括输出缓冲器满、外设响应、中断请求和是否允许发出中断请求。

方式2:A口可用,半双工,C口部分位(5位)提供应答联络,B口可以工作于方式0或方式1. 适用于中断、查询方式传输。

8253 定时器

三通道,每通道计数器16位。

8位数据总线,A0和A1选择片内端口。

每个计数器输入CLK计数和GATE触发,输出OUT. 初值写入初值寄存器,经过CLK的一个上升沿和一个下降沿后被装入减一计数器,需要读出时进当前数值锁存器。

计数器初值的最大值是0000H,因为是减一再判零。

读出计数器当前值包括一次写两次读:向控制口写锁存命令,读计数器端口(低八位),读计数器端口(高八位)。

工作方式

方式 触发方式 装入次数 GATE OUT 说明 方式0 自动触发 1次 1允许,0暂停 写控制字后0,计数结束后1 写入N后经过N+1个CLK周期OUT变高 方式1 硬件触发 多次 任何时候,GATE上升沿到达后,经过一个CLK上升和下降,初值被装入 写控制字后1,装入后0,计数结束后1 OUT负脉冲宽度为N个CLK 方式2 自动触发 多次 1允许,0暂停,由0变1重新计数 写控制字后1,计数器为1时0,计数结束1,反复 1/N分频器,负脉冲宽度1个CLK 方式3 自动触发 多次 1允许,0暂停,由0变1重新计数 写控制字后1,N/2或(N-1)/2时0,计数结束1,反复 占空比1:1的1/N分频器,0宽度小于等于1宽度 方式4 自动触发 1次 1允许,0暂停 写控制字后1,计数器0时0,之后1 写入N后经过N+1个CLK周期,负脉冲宽度1个CLK 方式5 硬件触发 多次 任何时候,GATE上升沿到达后,经过一个CLK上升和下降,初值被装入 写控制字后1,计数器0时0,之后1 写入N后经过N+1个CLK周期,负脉冲宽度1个CLK

8251 串行通信芯片

同步:码元同步、字符同步、帧同步。

- 异步串行:双方约定时钟频率,数据包按照一定标准编制。

- 同步串行:有专门的机制保持收发双方时钟同步。

异步串行通信标准

- 字符之间空闲位1.

- 一个起始位0.

- 5~8个数据位,从低位开始传送。

- 一个校验位,偶校验是指数据位和校验位一起1的个数为偶数,奇校验是指数据位和校验位一起1的个数为奇数。

- 1/1.5/2个停止位1.

- 如果码元宽度是时钟的16倍,则接收方在CLK上升沿采样,连续8个低电平认为是起始位,此后每16个CLK采样,就可以采在码元的中点。

- Buadrate:每秒传输的符号数,等于比特率,时钟频率是波特率的倍数(16、32、64等)。

调制解调:DA/AD转换,以正弦波传输,避免传输线效应导致边沿失真。

RS232C标准最小连线:TxD1RxD2,TxD2RxD1,SG1SG2.

8251一路发送一路接收,都有缓冲器。

8位数据总线,A0接选择片内端口。

发送数据写入缓冲器后TxRDY有效,接收数据写入缓冲器后RxRDY有效。

初始化约定:先向控制口写3个0,再写一个40H,执行软复位;然后写方式字,再写命令字。

8237A DMA控制器

DMA操作

- DMAC接受外设的DMA请求。

- DMAC向CPU发出总线请求。

- CPU发出总线响应后,DMAC接管总线,在地址总线上发出地址寄存器中的地址,并向外设发送DMA应答。

- DMAC给出IO和存储器的控制信号,在传输过程中对字节数计数。

- 交权。

4通道,可级联。

8位数据总线,8位地址总线。

页面寄存器:扩充地址的高4位或8位。

DREQDACKDMA请求和响应。HRQHLDA总线请求和响应。ADSTBA7-A0输出地址低8位,D7-D0输出高8位,由于数据总线复用了,ADSTB使外挂的地址锁存器将地址锁存。AEN总线独占信号,使CPU总线信号无效。工作模式

- 单字节传送:每次DMA传1个字节,当前地址寄存器和当前字节计数器自动修改,DMAC和CPU轮流控制总线,结束后输出EOP.

- 数据块传送:可以被EOP中止。

- 请求传输:DREQ=0时可以暂停,可以被EOP中止。

- 级联方式。

传送类型

- 读IO写MEM.

- 读MEM写IO.

- MEM到MEM,用通道0读,用通道1写,第一个DMA周期读到数据总线并存入内部暂存器,第二个周期内部暂存器写到数据总线。

优先级

- 固定。

- 循环,最近被服务过的最低。

编程步骤

- 主清除软命令。

- 写页面寄存器(地址的高4位)。

- 写当前地址(先低后高)。

- 写当前计数(先低后高)。

- 写模式寄存器。

- 写命令寄存器。

- 写屏蔽寄存器。

- 写请求寄存器。

总线

总线由传输信息的物理介质和一套管理信息传输的通用规则构成。

功能分类:数据总线、地址总线、控制总线、电源和地、备用线。

层次分类:片总线(片内总线、片间总线)、内总线、外总线。

总线操作过程

- 总线请求和仲裁:由主模块提出总线请求,由总线仲裁器分配。

- 寻址:取得使用权的主模块在地址总线发出从模块的地址。

- 传输。

- 结束:撤除相关信息,交权。